|

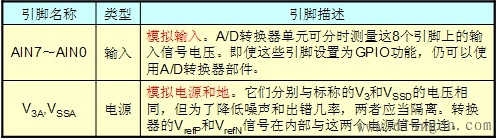

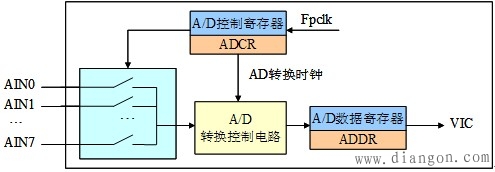

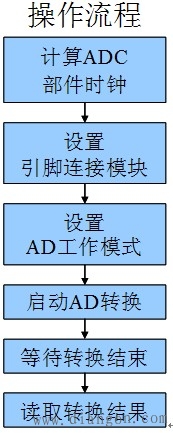

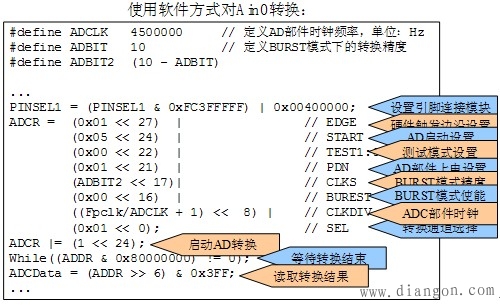

特性 LPC2114/2124具有一个AD转换器,LPC2200系列具有两个AD转换器,它们具有如下特性: 10位逐次逼近式模式转换器; 测量范围:0~3.3V; 10位转换事件>=2.44us; 可设置AD转换触发方式; 具有掉电模式。 A/D转换器描述 A/D转换器的基本时钟由VPB时钟提供。可编程分频器可将时钟调整至逐步逼近转换所需的4.5MHz(最大)。如要要得到10位精度的结果,需要11个A/D转换时钟。 A/D转换器的参考电压来自V3A和VSSA引脚。 A/D转换器描述 A/D引脚描述 |

|

|

A/D转换器内部结构 |

|

|

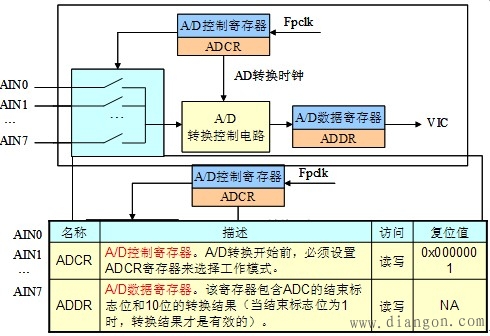

A/D转换器寄存器描述 |

|

|

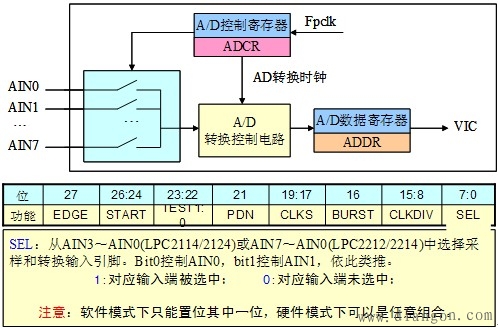

A/D转换器寄存器描述 ——控制寄存器 |

|

|

|

CLKDIV:将VPB时钟(PCLK)进行分频,得到AD转换时钟。分频后的时钟必须小于或等于4.5MHz。通常将CLKDIV编程为允许的最小值,以获得4.5MHz或稍低于4.5MHz的时钟。 |

|

|

CLKS:控制BURST模式下每次转换需要使用的时钟数和所得ADDR转换结果的LS位中可确保精度的位的数目,CLKS可在11个时钟(10位)~4个时钟(3位)之间选择:000=11个时钟/10位,001=10个时钟/9位,…111=4个时钟/3位。 |

|

|

V/VddA:当DONE位为1时,该字段包含对SEL字段选中的Ain脚的转换结果,为一个二进制数。 转换结果为0时,表示Ain引脚电平小于、等于或接近于VSSA。为0x3FF时,表示Ain引脚电平等于、大于或接近于VddA。输入电压计算公式为: Vin = 结果×(VSSA / 0x3FF) 0:这些位读出时为0。它们允许连续A/D值的累加,而不需要屏蔽处理,使得至少有256个值不会溢出到CHN字段。 CHN:该字段包含的是LS位的转换通道。 |

|

|

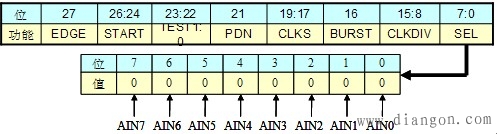

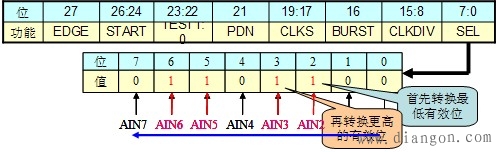

OVERUN:在BURST模式下,如果在转换产生最低位之前,以前转换的结果丢失或被覆盖,该位将置位。读ADDR寄存器时,该位清零。 DONE:AD转换完成标志位。当AD转换结束时该位置位。在读取ADDR或ADCR被写入时,该位清零。如果在转换过程中,设置了ADCR,那么该位将置位,并启动一次新的转换。 使用A/D转换器的注意要点 AD转换器的时钟不能大于4.5MHz; 使用MAT引脚触发AD转换启动时,相应的MAT信号不必输出到引脚。使用MAT引脚触发的方法,可以实现AD转换定时启动; BURST模式下,每次转换结束后立即开始下一路的转换,所以BURST模式具有最高的效率; 软件模式下,SEL字段中只能有一位置位,如果多位置位,将使用最低有效位。 A/D转换器操作示例 |

|

|

A/D转换器操作示例 |

|

电工学习网 ( )

GMT+8, 2021-12-6 20:44