|

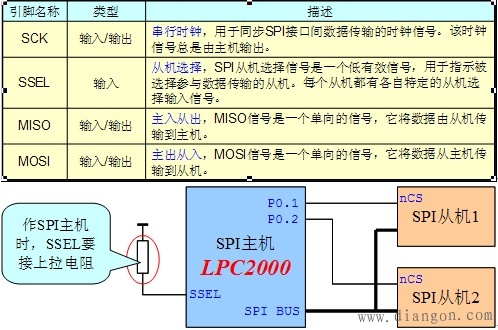

特性 大部分LPC2000系列微控制器具有两个硬件SPI接口(LPC2104/LPC2105/LPC2106只有一个),它们具有如下特性: 完全独立的SPI控制器; 遵循同步串行接口(SPI)规范; 全双工数据通信; 可配置为SPI主机或从机; 最大数据位速率为外设时钟Fpclk的1/8。 SPI简介 SPI是一种全双工的同步串行接口,一个SPI总线可以连接多个主机和多个从机。在同一时刻只允许一个主机操作总线,并且同时只能和一个从机通信。 串行时钟由主机产生,当主机发送一字节数据(通过MOSI)的同时,从机返回一字节数据(通过MISO)。 SPI电气连接 使用SPI通信需要4个引脚,分别为: |

|

|

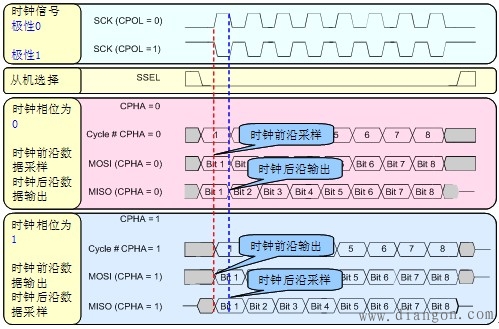

SPI传输时序 |

|

|

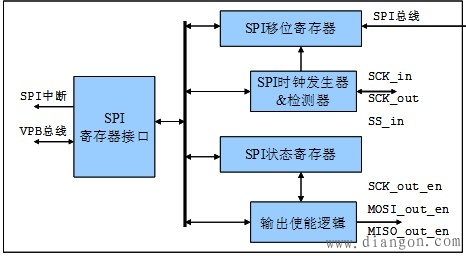

SPI工作模式 LPC2000在SPI通信中可作为从机也可以作为主机,这取决于硬件设计和软件设置。 当器件作为主机时,使用一个IO引脚拉低相应从机的选择引脚(SSEL),传输的起始由主机发送数据来启动,时钟(SCK)信号由主机产生。通过MOSI发送数据,同时通过MISO引脚接收从机发出的数据。 当器件作为从机时,传输在从机选择引脚(SSEL)被主机拉低后开始,接收主机输出的时钟信号,在读取主机数据的同时通过MISO引脚输出数据。 SPI接口内部结构 |

|

|

SPI寄存器描述 |

|

|

SPI寄存器描述 ——SPI控制寄存器 |

|

|

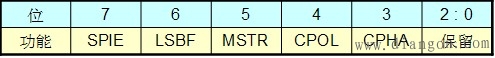

SPCR寄存器包含一些可编程位来控制SPI功能模块的功能,该寄存器必须在数据传输之前进行设定。 |

|

|

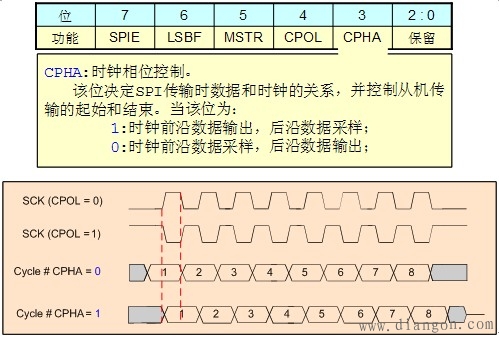

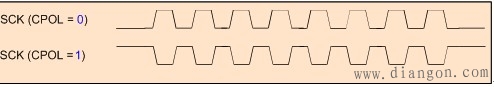

CPOL:时钟极性控制。 1:SCK为低有效; 0:SCK为高有效; |

|

|

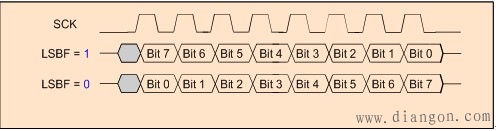

CPOL:主模式控制。 1:SPI处于主模式; 0:SPI处于从模式; LSBF:字节移动方向控制。 1:每字节数据从低位(LSB)开始传输; 0:每字节数据从高位(MSB)开始传输; |

|

|

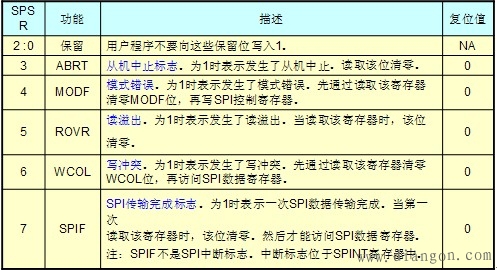

SPIE:SPI中断使能。 1:每次SPIF或MODF置位时都会产生硬件中断; 0:SPI中断被禁止; SPI寄存器描述 ——SPI状态寄存器 SPSR寄存器为只读寄存器,用于监视SPI功能模块的状态,包括一般性功能和异常状况。 |

|

|

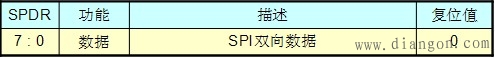

读溢出:当SPI功能模块内部读缓冲区包含没有读出的数据,而新的传输已经完成,就会发生读溢出。如果SPIF位置位 (读缓冲区已满),新接收到的数据将会丢失,而状态寄存器的读溢出(ROVR)位将置位。 写冲突:在SPI数据传输过程当中不应向SPI数据寄存器写入数据。不能向SPI数据寄存器写入数据的时间从传输启动时开始,直到SPIF置位时读取状态寄存器为止。如果在这段时间内写SPI数据寄存器,写入的数据将会丢失,状态寄存器中的写冲突位(WCOL)置位。 模式错误:SSEL信号在SPI功能模块为主机时必须无效,不能用作GPIO。当SPI功能模块为主机时,如果SSEL信号被激活(将SSEL变为低电平),表示有另外一个主机将该器件选择为从机。这种状态称为模式错误。 从机中止:如果SSEL信号在传输结束之前变为高电平,从传输将被认为中止。此时,正在处理的发送或接收数据都将丢失,状态寄存器的从机中止(ABRT)位置位。 SPI寄存器描述 ——SPI数据寄存器 SPDR寄存器为SPI提供数据的发送和接收。处于主模式时,向该寄存器写入数据,将启动SPI数据传输。从数据传输开始到SPIF状态位置位并且没有读取状态寄存器的这段时间内不能对该寄存器执行写操作。 |

|

|

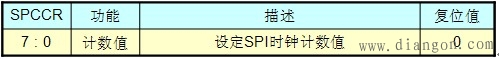

SPI寄存器描述 ——SPI时钟计数寄存器 作为主机时,SPCCR寄存器控制SCK的频率。寄存器的值为一位SCK时钟所占用的PCLK周期数。该寄存器的值必须为偶数,并且必须不小于8。如果寄存器的值不符合以上条件,可能会导致产生不可预测的动作。 SPI速率 = Fpclk / SPCCR |

|

|

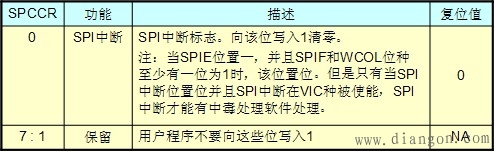

SPI寄存器描述 ——SPI中断寄存器 该寄存器包含SPI接口的中断标志。 |

|

|

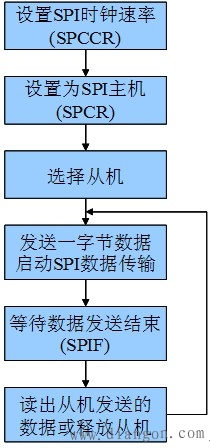

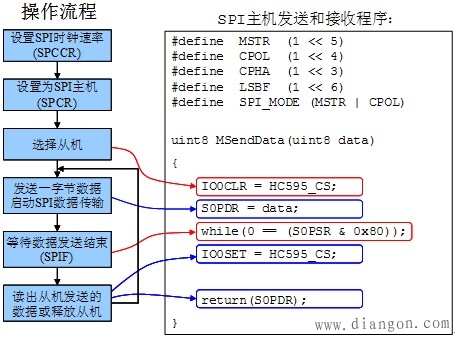

使用SPI接口的注意要点 作主机时,SSEL引脚必须接上拉电阻,不能作为IO口使用; 作主机时,在发送一字节数据的同时接收一字节数据; SPI时钟分频值必须大于或等于8; 数据寄存器与内部移位寄存器之间没有缓冲区,写SPDR会使数据直接进入移位寄存器。因此数据只能在上一次数据发送完成后写入SPDR寄存器。 SPI应用示例 ——作为主机 |

|

|

|

|

|

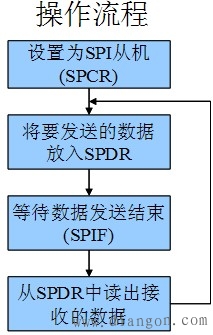

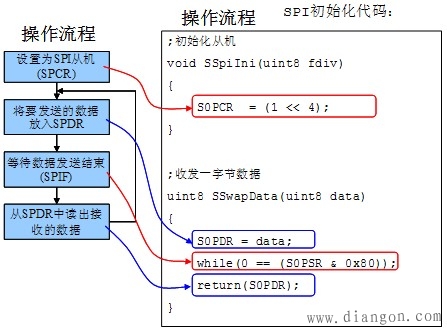

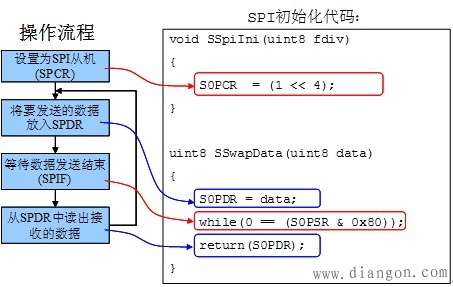

SPI应用示例 ——作为从机 |

|

|

电工学习网 ( )

GMT+8, 2021-12-6 20:44