|

相关寄存器 外部存储器控制器包含4个寄存器,它们分别对应一个存储器组。通过这些寄存器,可以分别设置每个存储器组读写访问之间插入的等待周期个数、每个存储器组的总线宽度等。 |

|

|

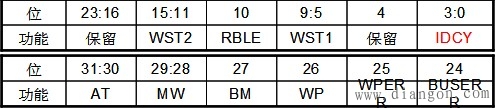

存储器组配置寄存器0~3(BCFG0~3): |

|

|

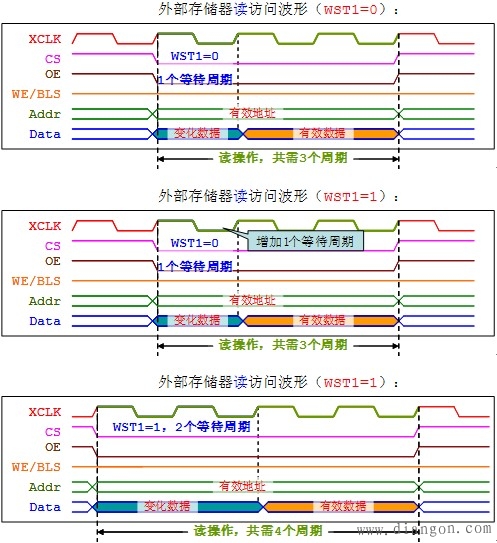

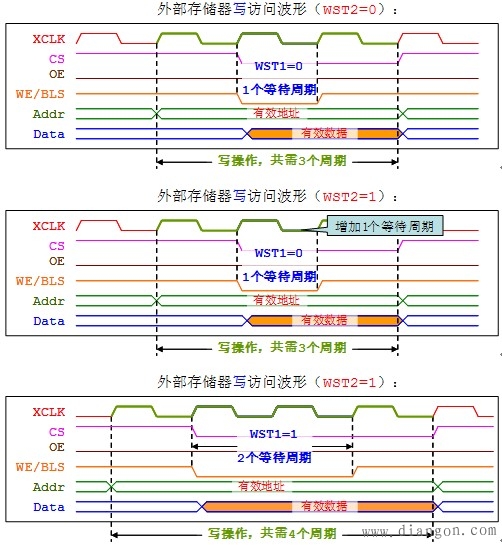

IDCY:在两个存储器组之间切换访问时,为了避免器件间的总线竞争,需要插入空闲的CCLK周期,该域控制着这个周期数。 计算公式为:空闲CCLK周期数 = IDCY +1;(IDCY的复位值为15) WST1:一些慢速的外部存储器可能不能适应EMC最高速度的读操作,所以需要在读周期中插入若干个空闲等待周期,以降低读操作的速度。该域控制着读周期中插入的空闲CCLK周期数。 计算公式为:读操作周期长度 = WST1 + 3;(WST1的复位值为15) |

|

|

RBLE:如果外部存储器的总线宽度为16或32位,那么读写操作是对总线上的2个或4个字节的数据同时进行的。某些存储器允许对总线上的某几个字节进行独立的读写操作,而不影响其它字节,这通过芯片的字节定位引脚实现。当RBLE位为1时使能字节定位功能,BLS3:0在读写操作时输出低电平。当RBLE位为0时,禁止该功能。 |

|

|

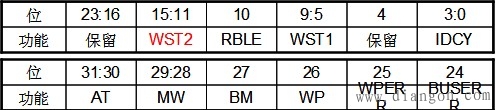

存储器组配置寄存器0~3(BCFG0~3): |

|

|

WST2:和读操作类似,一些慢速的外部存储器可能不能适应EMC最高速度的写操作,所以需要在写周期中插入若干个空闲等待周期,以降低写操作的速度。该域控制着写周期中插入的空闲CCLK周期数。 计算公式为:写操作周期长度 = WST2 + 3;(WST2的复位值为15) 对于Burst ROM,计算公式为:写操作周期长度 = WST2 + 1; |

|

|

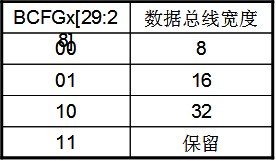

BUSERR:总线错误状态位。如果EMC检测到AMBA总线上出现一个大于32位数据访问的请求,那么该位将置位。ARM7TDMI-S内核不会出现这样的请求; WPERR:错误写状态位。如果对一个已经写保护(WP位为1)的存储器组进行写操作,该位将置位。向该位写入1,可以清零该位。 WP:该位为1时,相应的存储器组被写保护; BM:如果外部存储器使用了Burst ROM,将该位置1; AT:该域通常写入00。 MW:该位控制相应存储器组的数据总线宽度,如下表所示。 |

|

|

MW控制域(BCFG[29:28])与引脚BOOT1:0的关系: 由于Bank0可用于引导程序运行,所以BCFG0[29:28]的复位值与引脚BOOT1:0的设定有关(当BOOT1:0=11时,复位后从片内Flash引导程序运行)。 |

|

|

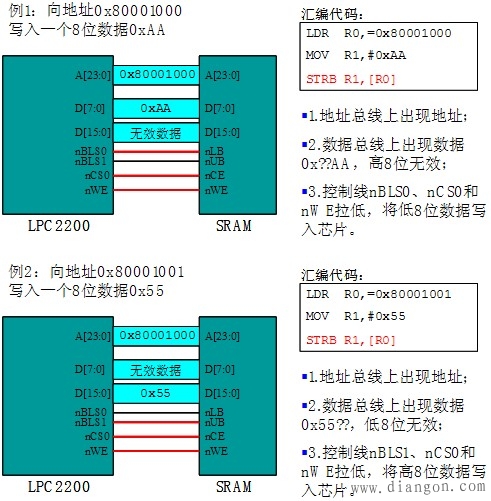

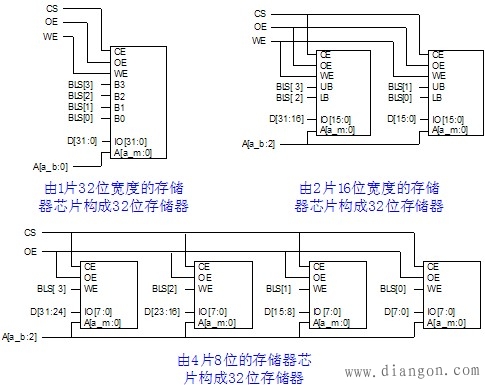

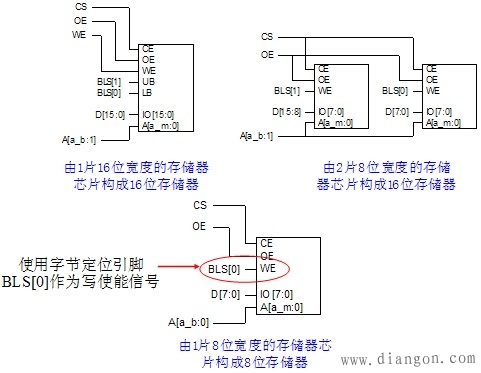

与外部存储器的连接 如果存储器组配置成32位宽度,地址线A0和A1无用,可作为GPIO使用(由PINSEL2设置); 如果存储器组配置成16位宽度,地址线A0无用,可作为GPIO使用(由PINSEL2设置); 如果存储器组配置成8位宽度,并且使能字节定位功能(RBLE=1),存储器的写信号由 BLS[0]提供,否则由WE信号提供; 同一寄存器组的器件宽度必须一致。 与外部存储器连接——32位宽度 |

|

|

与外部存储器连接——8/16位宽度 |

|

|

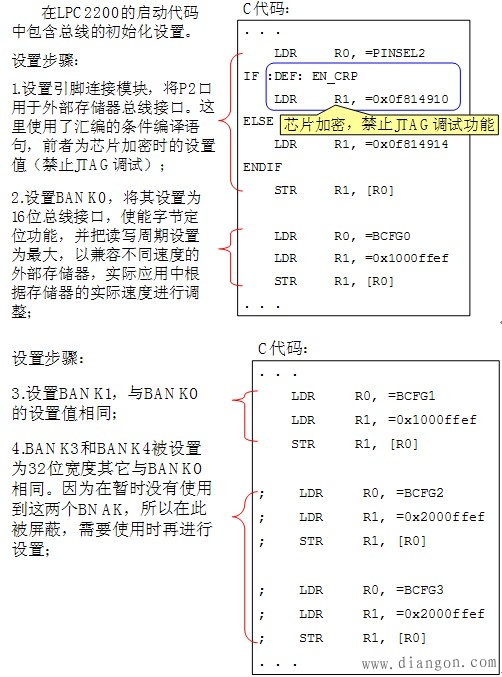

相关启动代码分析 |

|

电工学习网 ( )

GMT+8, 2021-12-6 20:44