|

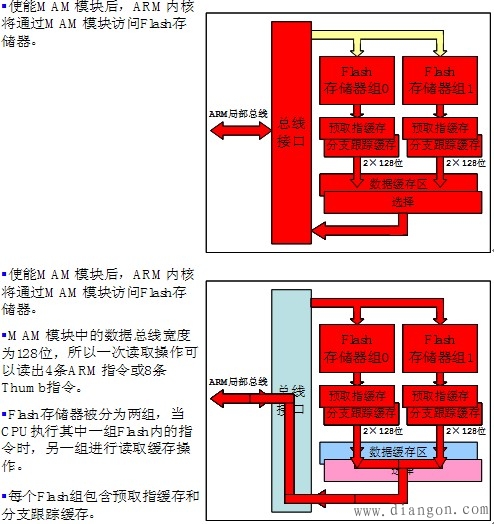

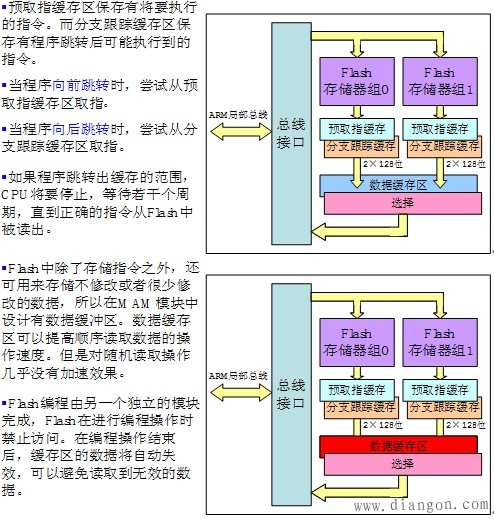

LPC2114/2124/2210/2212/2214微控制器的ARM内核工作在最高频率60MHz时,执行一条指令约为17ns。而Flash存储器的访问周期需要50ns,即最高频率20MHz。所以如果将代码存放在Flash中,将影响ARM内核发挥最大效能。为了能将指令从内部Flash存储器更高效快速地提取到ARM内核,而设计产生了一个存储器加速模块(MAM)。 MAM结构 |

|

|

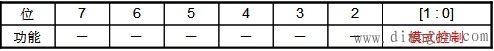

| 存储器加速模块寄存器描述 MAM控制寄存器(MAMCR): |

|

|

MAMCR[1:0]:用于MAM的模式控制,具体关系如下表。 |

|

|

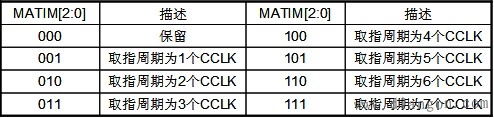

存储器加速模块寄存器描述 MAM定时寄存器(MAMTIM): |

|

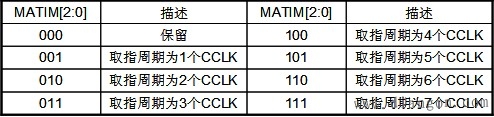

MAMTIM[2:0]:决定使用多少个CCLK周期访问Flash存储器,这样可以调整MAM时序使其匹配处理器操作频率,具体关系如下表。 |

|

|

当访问周期设置为1个CCLk时,实际上关闭了MAM,但是仍可以选择MAM模式对功耗进行优化。 注意:不正确的设定会导致器件的错误操作 |

|

|

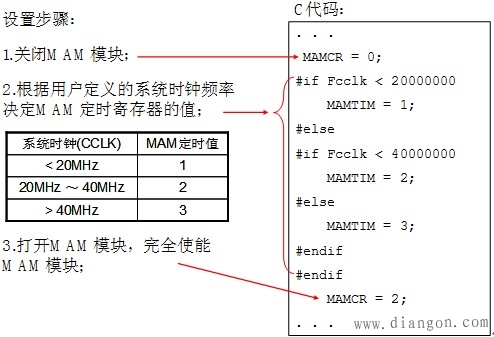

MAM使用要点 当改变MAM定时值时,必须先将MAMCR设置为0关闭MAM,然后将新值写入MAMTIM。最后将需要的操作模式的对应值(1或2)写入MAMCR,再次打开MAM; 对于低于20MHz的系统时钟,MAMTIM设定为001,将Flash访问时间设定为1CCLK ;对于20MHz到40MHz之间的系统时钟,建议将Flash访问时间设定为2CCLK;高于40MHz的系统时钟,建议使用3CCLK。 相关启动代码分析 |

|

|

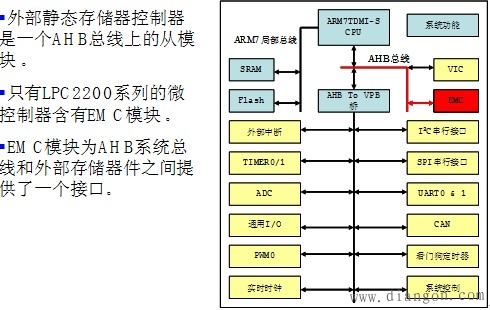

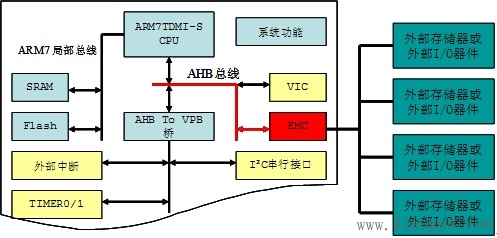

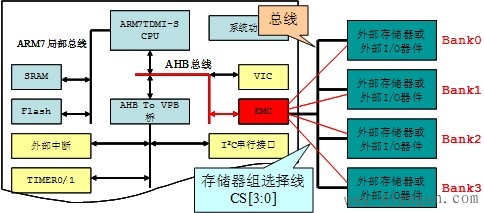

外部存储器控制器概述 |

|

|

|

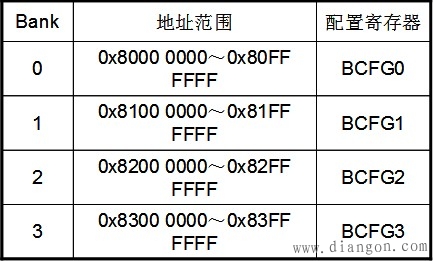

EMC模块支持4个独立配置的存储器组,每个存储器组的总线宽度可设置为8、16或者32位,但是同一个存储器组的器件必须宽度相同。 每个存储器组最大支持16MB寻址空间。 支持字节定位读取。 |

|

|

地址输出线是A[23:0],其中地址位A[25:24]用于4个存储器组的译码(CS[3:0])。 |

|

|

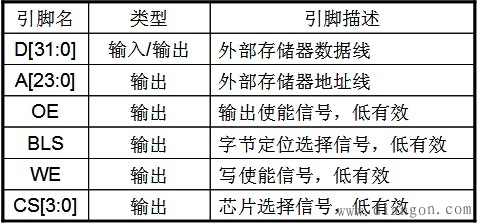

外部存储器总线接口描述 接口引脚描述: |

|

|

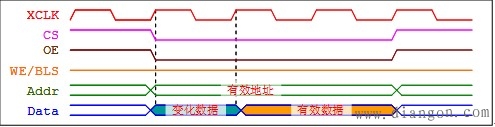

这些引脚与P1、P2和P3口GPIO功能复用,所以在使用外部总线前首先要正确设置PINSEL2寄存器。可以在硬件上对引脚BOOT1:0设定,复位时微处理器自动初始化PINSEL2。或者在软件上字节初始化PINSEL2,这只适用于片内FLASH引导程序运行的系统中。 外部存储器读访问典型波形: |

|

|

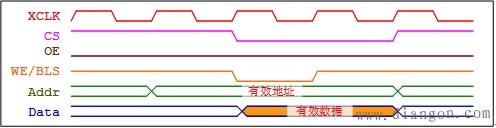

经过一个等待状态后,存储器输出有效数据。 外部存储器写访问典型波形: |

|

电工学习网 ( )

GMT+8, 2021-12-6 20:44